Проходной USB-шифратор флэш-дисков

Проходной USB-шифратор флэш-дисков

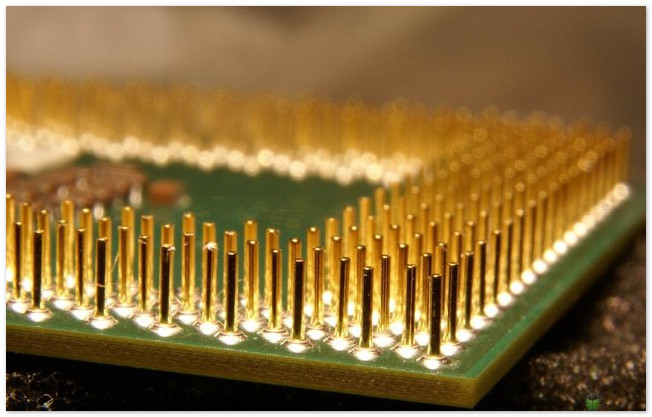

В современных компьютерах USB-контроллер встроен в системную плату. Он представляет собой угрозу безопасности компьютера, поскольку стандартные средства Windows не позволяют пользователям контролировать передачу информации через интерфейс USB. Обычные USB флэш-диски можно использовать для безопасного хранения и перемещения небольших объёмов информации. Для этого данные должны записываться на носитель в зашифрованном виде. С целью решения перечисленных ве задач был разработан проходной USB-шифратор флэш-дисков. Он обеспечивает аппаратное шифрование всех данных, передаваемых от хост-контроллера USB к флэш-диску и обратно. Доступ к компьютеру ограничен с помощью электронного замка -специального аппаратно-программного модуля. USB-шифратор разрывает физическую связь уровня интерфейса и логическую связь уровня устройства, в этот разрыв устанавливается система взаимодействия связей шифратора USB. Схемотехническая реализация проходного USB-шифратора включает в себя два USB-контроллера один обрабатывает запросы хост-контроллера системной платы, передаёт их шифропроцессору, и далее другому контроллеру, который взаимодействует непосредственно с флэш-диском; и шифропроцессор непосредственно он и шифрует данные, пропуская при этом команды насквозь без шифрования; а модуль управления и безопасности управляет работой всех устройств на плате, обеспечивает защищенный приём ключей с ключевого носителя, включает в себя датчик случайных чисел; энергонезависимая память шифратора обеспечивает хранение системного ПО платы, которое запускается во время инициализации шифратора.

Распределители сигналов для систем обработки цифровых потоков информации

Распределители сигналов (далее сокращённо PC) являются обязательной составной частью практически любой системы обработки цифровых потоков информации. PC преобразуют временно-импульсный код в пространственно-временной код. В некоторых системах обработки цифровых потоков информации наряду с PC жёсткой структуры необходимо иметь схемы PC с возможно стью циклического изменения их структуры. В системах обработки цифровых потоков видеоинформации (далее сокращённо ЦПВИ) найдут применение PC на основе счётчиков с программируемой последовательностью импульсов (далее сокращённо РСППИ). Современные СБИС программируемой логики семейства Virtex- имеют уровень интеграции несколько миллионов эквивалентных вентилей на одном кристалле и системные, частоты до 420 МГц. Их применение позволило изменить подход к проектированию аппаратуры обработки (сжатия) ЦПВИ, т.к. в данных СБИС практически снимается требование по минимизации используемых в РСППИ количества вентилей на один разряд счётчика. Авторами разработан специальный счётчик, предназначенный для применения в РСППИ (Счётчик Кузьмичёва) относится к классу счётчиков 1 из N. Наряду со схемами РСППИ прямого счёта, в схемотехнике систем обработки ЦПВИ могут найти применение реверсивные счётчики -распределители. Для обеспечения реверсивного режима работы РСППИ, в каждый канал (разряд), его счётчика, дополнительно введена цепь реверсивного управления, имеющая свой вход разрешения счёта и выход переноса. РСППИ может корректно работать на частоте порядка 1,25 ГГц.

Усовершенствование модуля последовательного преобразования для процессора

Целью данного исследования является усовершенствование модуля последовательного преобразования. В современных процессорах часто присутствуют последовательный интерфейс и выход широтно-импульсной модуляции. Они обычно выполняются как два разнородных блока. При этом каждый из них выполняет строго ограниченные функции. Учитывая, что в основе и того и другого устройства лежит метод последовательного преобразования, основанный на поразрядном уравновешивании, можно разработать единый блок, который реализует оба интерфейса, а также другие, основанные на этом методе. Сюда входят, например преобразования в код Фибоначчи, R-кодирование, FM и MFM. Данный универсальный метод поразрядного уравновешивания известен в литературе как метод нумерационного кодирования, предложенный в начале 70-х годов независимо Бабкиным и Кавером. Этот метод основан на подсчете числа последовательностей с заданным префиксом. Сложность метода заключается в анализе этого префикса и уменьшении объемов , адресуемых этим префиксом. В настоящее время предложено значительное количество методов, которые позволяют обойтись без этих , этим самым уменьшить емкостную сложность устройств. Префикс заменяется набором небольшого количества переменных (генерируемых счетчиками) над которыми проводятся элементарные математические операции (сложение, вычитание). Появилось значительное количество работ Имминг, Колесник, Васильев, Браун, Шалкенс, Курмаев. Таким образом, предложенный метод позволяет уменьшить сложность устройств и увеличить их функциональность. В статье решены вопросы разработки модуля последовательного преобразования с расширенной функциональностью.

Проблема эффективного управления потребителями электроэнергии

В современных системах контроля электротехнического оборудования остро стоит проблема эффективного управления потребителями электроэнергии. Широко используемые в настоящее время релейные системы коммутации имеют ряд существенных недостатков искрение при включениивыключении, эффект дребезга контактов, создание в сети импульсных помех. Для устранения описанных недостатков применяются электронные коммутирующие устройства (тиристоры, семг сторы). Для правильного управления электронными коммутирующими устройствами, а также для возможно й фазовой регулировки мощности, необходима точная привязка к фазе сети. Наиболее перспективным и простым в применении способом фазовой привязки является программная реализация ФАПЧ. Основной проблемой при реализации программной ФАПЧ является наличие в электросети общего пользования различного рода помех. Для построения системы с использованием программного метода ФАПЧ может использоваться стандартный микроконтроллер с 10-разрядным встроенным АЦП. Входной сигнал оцифровывается с частотой 10 кГц. Для получения знаковых величин из каждого оцифрованного значения вычитается текущее значение уровня нуля. Алгоритм программной ФАПЧ состоит из двух взаимосвязанных частей захват фазы и корректировка уровня нуля. Для захвата фазы анализируется сумма выходных значений с АЦП за полупериод. В зависимости от полученных значений меняются интервалы оцифровки входного сигнала. Корректировка уровня нуля делается на основе анализа суммарных значений с АЦП за период. При этом вновь вычисленный уровень нуля используется в дальнейшем для получения знаковых величин с АЦП. Описанный метод программной ФАПЧ позволяет при низкой производительности процессора производить устойчивое и непрерывное управление подключенным электротехническим оборудованием.

Принципы асинхронного проектирования и информационная структура алгоритма

Обмен данными в синхронных системах привязан к тактам и маркируется сигналами значимости, в асинхронных системах основа протокола — алгоритм рукопожатия. Основой спецификации асинхронных протоколов является граф STG, в которых переходы интерпретируются как изменения состояния цепей. В был сделан анализ перехода от алгоритма к аппаратному планированию через анализ информационной структуры алгоритма (ИСА), представляющий алгоритм как набор элементарных действий и графом подстановок между ними. Автор этой статьи задался целью исследовать, возможен ли переход от ИСА к автоматической генерации асинхронной логики управления ИСА. Существует переход от STG-описания (Signal Transition Graph) к схемной реализации асинхронной логики управления. При этом существуют несколько логических проблем, которые разрешаются за приемлемое время программным обеспечением Petrify только для малых STG-схем. Например, асинхронная логика управления для простейшего регистрового сумматора синтезировалась 30 минут (на Pentium 3, 800 МГц). Поэтому актуален вопрос декомпозиции ИСА на элементарные операции, для которых время синтеза будет приемлемым. статья будет посвящен описанию технологии перехода от STG к синтезируемым логическим функциям и декомпозиционному анализу информационной структуры алгоритма Peter A et aPBridging the gap between asynchronous design and designers, hi.upc.es4ordicfpubHcationstutorials.html. Лялин А.С. Информационная технология От алгоритма к аппаратуре на примере аппаратной реализации БПФ Сборник научных трудов МФТИ Моделирование процессов управления, М2004.

Координатная система контроля движущихся объектов

Рассматривается координатная система, представляющая собой матрицу фото датчиков ультрафиолетового (УФ) излучения на основе нитрида алюминия (A1N) и пленочных датчиков излучения инфракрасного (ИК) диапазона. Ультрафиолетовый датчик представляет собой две шины и матрицу с построчным параллельным соединением емкостей, а датчик инфракрасного излучения последовательное соединение термопар. Координатная система строится следующим образом. Датчики УФ излучения представлены матрицей из N х N элементов, а датчики ИК излучения располагаются между датчиками УФ с чередованием строк и столбцов. Матрица датчиков УФ излучения делится на квадранты. При перемещении цели изменяется выходной сигнал. Данный способ построения координатной системы делает возможным создание комбинированной системы обнаружения движущихся объектов.

Рубрика: Обзоры